# Low Capacitance Surface Mount TVS for High-Speed Data Interfaces

The NUP4201DR2 transient voltage suppressor is designed to protect equipment attached to high speed communication lines from ESD, EFT, and lightning.

#### Features:

- SO–8 Package

- Peak Power 500 Watts 8 x 20 µS

- ESD Rating: IEC 61000–4–2 (ESD) 15 kV (air) 8 kV (contact) IEC 61000–4–4 (EFT) 40 A (5/50 ns) IEC 61000–4–5 (lightning) 23 (8/20 μs)

- UL Flammability Rating of 94V–0

#### **Typical Applications:**

- High Speed Communication Line Protection

- USB Power and Data Line Protection

- Video Line Protection

- Base Stations

- HDSL, IDSL Secondary IC Side Protection

- Microcontroller Input Protection

### MAXIMUM RATINGS

| Rating                                                                    | Symbol                            | Value          | Unit |

|---------------------------------------------------------------------------|-----------------------------------|----------------|------|

| Peak Power Dissipation<br>8 x 20 $\mu$ S @ T <sub>A</sub> = 25°C (Note 1) | P <sub>pk</sub>                   | 500            | W    |

| Junction and Storage<br>Temperature Range                                 | T <sub>J</sub> , T <sub>stg</sub> | –55 to<br>+150 | °C   |

| Lead Solder Temperature –<br>Maximum 10 Seconds Duration                  | ΤL                                | 260            | °C   |

1. Non-repetitive current pulse 8 x 20 µS exponential decay waveform

## ON Semiconductor®

http://onsemi.com

## SO-8 LOW CAPACITANCE VOLTAGE SUPPRESSOR 500 WATTS PEAK POWER 6 VOLTS

CASE 751 PLASTIC

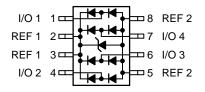

## MARKING DIAGRAM

#### **ORDERING INFORMATION**

| Device     | Package | Shipping <sup>†</sup> |

|------------|---------|-----------------------|

| NUP4201DR2 | SO-8    | 2500/Tape & Reel      |

<sup>+</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

### **ELECTRICAL CHARACTERISTICS**

| Characteristic                                               | Symbol          | Min | Тур | Max | Unit |

|--------------------------------------------------------------|-----------------|-----|-----|-----|------|

| Reverse Breakdown Voltage @ $I_t = 1.0 \text{ mA}$           | V <sub>BR</sub> | 6.0 | -   | -   | V    |

| Reverse Leakage Current @ V <sub>RWM</sub> = 5.0 Volts       | I <sub>R</sub>  | N/A | -   | 10  | μΑ   |

| Maximum Clamping Voltage @ $I_{PP}$ = 1.0 A, 8 x 20 $\mu$ S  | V <sub>C</sub>  | N/A | -   | 9.8 | V    |

| Maximum Clamping Voltage @ I <sub>PP</sub> = 10 A, 8 x 20 μS | V <sub>C</sub>  | N/A | -   | 12  | V    |

| Between I/O Pins and Ground @ DC Bias = 0 V, 1.0 MHz         | Capacitance     | -   | 5.0 | 10  | pF   |

| Between I/O Pins and I/O @ DC Bias = 0 V, 1.0 MHz            | Capacitance     | -   | 2.5 | 5.0 | pF   |

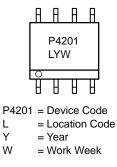

### ELECTRICAL CHARACTERISTICS

$(T_A = 25^{\circ}C \text{ unless otherwise noted})$ UNIDIRECTIONAL (Circuit tied to Pins 1 and 3 or 2 and 3)

| Symbol           | Parameter                                                 |  |  |

|------------------|-----------------------------------------------------------|--|--|

| I <sub>PP</sub>  | Maximum Reverse Peak Pulse Current                        |  |  |

| V <sub>C</sub>   | Clamping Voltage @ IPP                                    |  |  |

| V <sub>RWM</sub> | Working Peak Reverse Voltage                              |  |  |

| I <sub>R</sub>   | Maximum Reverse Leakage Current @ V <sub>RWM</sub>        |  |  |

| V <sub>BR</sub>  | Breakdown Voltage @ I <sub>T</sub>                        |  |  |

| Ι <sub>Τ</sub>   | Test Current                                              |  |  |

| $\Theta V_{BR}$  | Maximum Temperature Coefficient of VBR                    |  |  |

| ١ <sub>F</sub>   | Forward Current                                           |  |  |

| VF               | V <sub>F</sub> Forward Voltage @ I <sub>F</sub>           |  |  |

| Z <sub>ZT</sub>  | Z <sub>ZT</sub> Maximum Zener Impedance @ I <sub>ZT</sub> |  |  |

| I <sub>ZK</sub>  | Reverse Current                                           |  |  |

| Z <sub>ZK</sub>  | Maximum Zener Impedance @ I <sub>ZK</sub>                 |  |  |

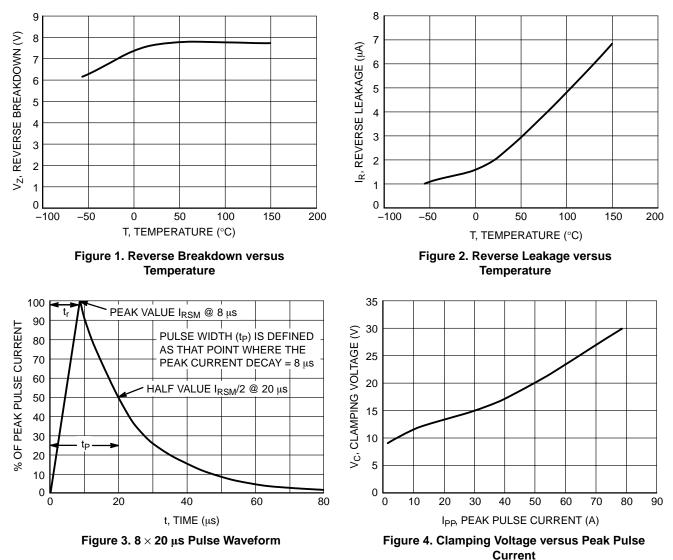

## **TYPICAL CHARACTERISTICS**

#### APPLICATIONS INFORMATION

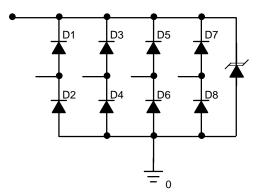

The new NUP4201DR2 device is a low capacitance TVS Diode array designed to protect sensitive electronics such as communications systems, computers, and computer peripherals against damage due to ESD conditions or transient voltage conditions. Because of its low capacitance array configuration, it can be used in high speed I/O data lines.

The integrated design of the NUP4201DR2 device offers surge rated, low capacitance steering diodes and a TVS diode integrated in a single package (SO-8). If a transient condition occurs, the steering diodes will drive the transient condition to the positive polarity of the power supply or to ground. The TVS device protects the power line against over–voltage conditions to avoid damage in any downstream components.

#### NUP4201DR2 Device's Configurations Options

The NUP4201DR2 is able to protect up to four data lines against transient over-voltage conditions by driving them to a fixed reference point for clamping purposes. The steering diodes will be forward biased whenever the voltage on the protected line exceeds the reference voltage (Vcc+Vf). The diodes will drive the transient current away from the sensitive circuit.

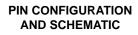

Data lines are connected at pins 1,4,6 and 7. The negative reference is connected at pins 5 and 8. These pins must be connected directly to ground by using a ground plane to minimize the PCB's ground inductance. It is very important to reduce as much as possible the PCB trace lengths to minimize parasitic inductances.

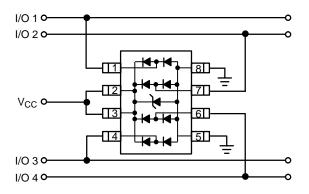

#### **Option 1**

Four Data lines protection and power supply protection using Vcc as reference.

For this configuration, connect pins 2 & 3 directly to the positive supply rail (Vcc), the data lines are referenced to the supply voltage. The internal TVS diode prevents over–voltage on the supply rail.

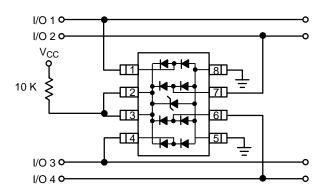

#### Option 2

Four Data lines protection with Bias and power supply isolation resistor.

The NUP4201DR2 device can be isolated from the power supply by connecting a series resistor between pins 2 & 3 and Vcc. A resistor of  $10K\Omega$  is recommended for isolation purposes. The internal TVS and steering diodes remain biased, which provides the advantage of lower capacitance.

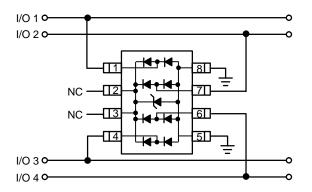

#### **Option 3**

Four Data lines protection using internal TVS diode as reference.

In the case of applications in which a positive supply reference is not available or full isolation is required, the internal TVS could be used as the reference, so for this purpose, the pins 2 and 3 are not connected. In this case, the steering diodes will conduct whenever the voltage on the protected line exceeds the working voltage of the TVS plus one diode drop (Vc=Vf + VTVS).

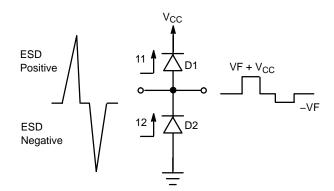

#### "Rail to Rail" Protection Topology

The following figure shows a case when discrete diodes are configured for rail to rail protection on an I/O line:

Upon the above figure, it is possible to observe that if a positive ESD condition occurs, the D1 diode will be forward biased while the D2 diode will be biased when a negative ESD condition occurs. A valid first approximation of the resulting clamping voltage due to the protection diodes can be made as follows:

For positive pulse conditions:

Vc = Vcc + Vf

For negative pulse conditions:

Vc = -Vf

It is important to mention that effects of parasitic inductances must be considered for fast rise time transient conditions because the clamping voltage on the protected circuit will be different than in the previous case. A valid approximation of the resulting clamping voltage can be made as show below:

For positive pulse conditions:

Vc = Vcc + Vf + (L diesd/dt)

For negative pulse conditions:

Vc = -Vf - (L diesd/dt)

As shown in the formulas, the clamping voltage (Vc) not only depends on the Vf of the steering diodes but also in the L diesd/dt factor, so this is why it is very important to have a good board layout to minimize the effects of the parasitic inductances.

Nevertheless, some disadvantages are still present when discrete diodes are used to suppress ESD conditions in "rail to rail" configuration. If the ESD current is too high, it can potentially result in the damage of any components connected to that rail and it is also possible to experience damage in the discrete diodes if their power dissipation capability is exceeded.

The NUP4201DR2 On Semiconductor's device provides a concept named "RailClamp" which is designed to eliminate the disadvantages of the usage of discrete diodes for ESD protection. The RailClamp concept is achieved with the integration of the TVS device in together with the steering diodes.

Rail to Rail Protection with integrated TBS to achieve the RailClamp concept

During an ESD condition, the ESD current will be driven to ground through the TVS device, so the resulting clamping voltage on the protected IC will be:

Vc = VF(RailClamp) + VTVS.

The clamping voltage of the TVS device is shown as part of the specifications of the NUP4201DR2 datasheet. The clamping voltage will depend on the magnitude of the ESD current. The steering diodes are fast switching devices with unique forward voltage and low capacitance characteristics.

## **TYPICAL APPLICATIONS**

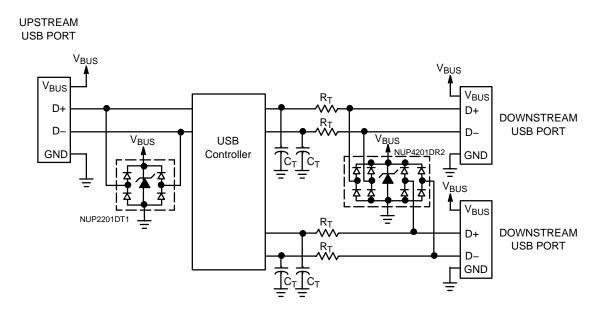

ESD Protection for USB Port

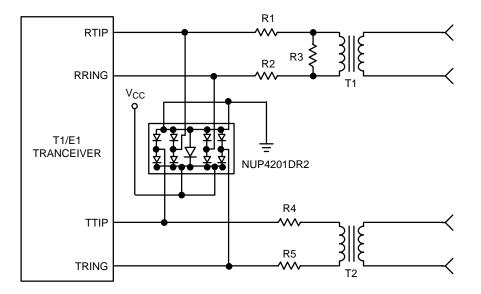

**TI/E1 Interface Protection**

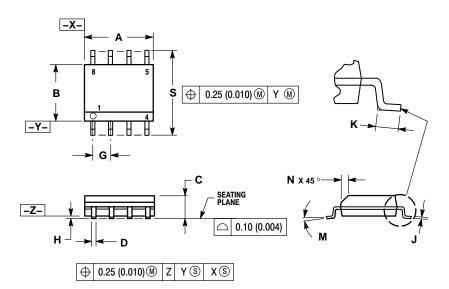

#### PACKAGE DIMENSIONS

SO-8 CASE 751-07 ISSUE AB

NOTES:

- NOTES:

DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

751-01 THRU 751-06 ARE OBSOLETE. NEW STANDAARD IS 751-07

|     | MILLIMETERS |          | INCHES |           |  |  |

|-----|-------------|----------|--------|-----------|--|--|

| DIM | MIN         | MAX      | MIN    | MAX       |  |  |

| Α   | 4.80        | 5.00     | 0.189  | 0.197     |  |  |

| В   | 3.80        | 4.00     | 0.150  | 0.157     |  |  |

| С   | 1.35        | 1.75     | 0.053  | 0.069     |  |  |

| D   | 0.33        | 0.51     | 0.013  | 0.020     |  |  |

| G   | 1.2         | 1.27 BSC |        | 0.050 BSC |  |  |

| Н   | 0.10        | 0.25     | 0.004  | 0.010     |  |  |

| J   | 0.19        | 0.25     | 0.007  | 0.010     |  |  |

| K   | 0.40        | 1.27     | 0.016  | 0.050     |  |  |

| М   | 0 °         | 8 °      | 0 °    | 8 °       |  |  |

| N   | 0.25        | 0.50     | 0.010  | 0.020     |  |  |

| S   | 5.80        | 6.20     | 0.228  | 0.244     |  |  |

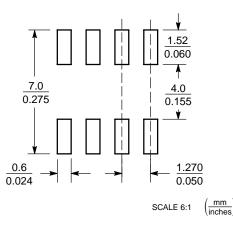

**SOLDERING FOOTPRINT\***

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters which may be rovided in solut. C add sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters which may be provided in solut. C and the solut. C products of the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications in which the Failure of the SCILLC product cauld create a situation where personal nipury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051 Phone: 81–3–5773–3850 ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.